Memory Locality

Spatial locality - If a memory location is referenced once, the the program is likely to reference a nearby memory location in the near future

Temporal locality - A memory location that is referenced once is likely to be referenced again multiple times in the near future

Memory locality means that to increase performance, accesses should be satisfied by upper memory layers

Memory Hierarchy And Management

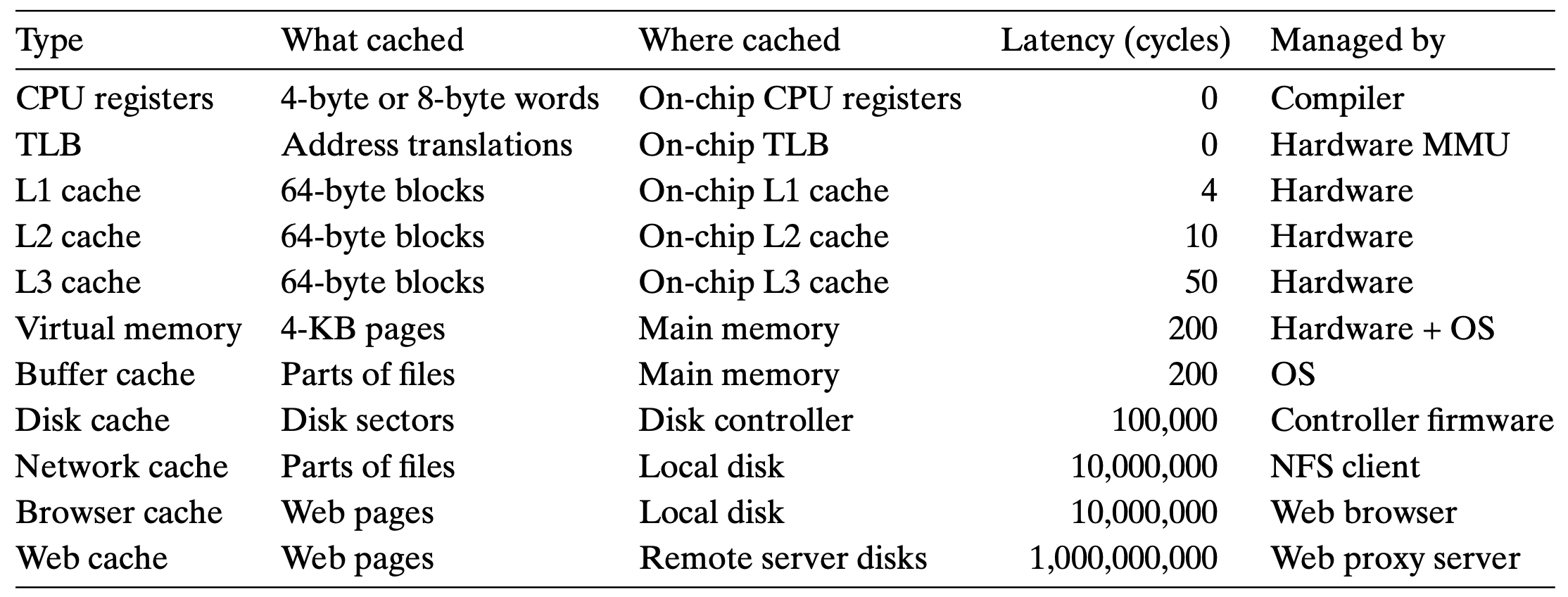

Upper layers typically store smaller subsets of data from lower layers but have faster access. Due to locality, accesses are often satisfied by upper layers

Memory management:

Data Transfer Units

Data is always copied back and forth between level and level in block-size transfer units:

- From L1 cache to registers in 64-bits words

- From lower cache to higher level cache in 64-bytes cache data blocks

- From RAM to cache in 64-bytes cache data blocks

- From disk to RAM in disk blocks

Example of a Memory Flow

Memory flow during execution of the statement int x = 10:

- Virtual address to physical address conversion (TLB lookup)

- TLB miss

- TLB update (might involve OS)

- OS may need to swap in page to get the appropriate page table (load from disk to physical address)

- Cache lookup (tag check)

- Determine line not in cache (need to generate read-miss)

- Arbitrate for bus

- Win bus, place address, command on bus

- All caches perform snoop (e.g., invalidate their local copies of the relevant line)

- Another cache or memory decides it must respond (let’s assume it’s memory)

- Memory request sent to memory controller

- Memory controller is itself a scheduler

- Memory controller checks active row in DRAM row buffer. (May need to activate new DRAM row. Let’s assume it does.)

- DRAM reads values into row buffer

- Memory arbitrates for data bus

- Memory wins bus

- Memory puts data on bus

- Requesting cache grabs data, updates cache line and tags, moves line into exclusive state

- Processor is notified that data exists

- Instruction proceeds

References

- Computer Systems A Programmer’s Perspective, Global Edition (3rd ed). Randal E. Bryant, David R. O’Hallaron

- Snooping-Based Cache Coherence: CMU 15-418/618 Spring 2016

- Directory-Based Cache Coherence: CMU 15-418/618 Spring 2016

- A Basic Snooping-Based Multi-Processor Implementation: CMU 15-418/618 Spring 2016